# High-Efficiency GaAs-Based *p*HEMT C-Band Power Amplifier

J. J. Brown, J. A. Pusl, M. Hu, A. E. Schmitz, D. P. Docter, J. B. Shealy, M. G. Case, M. A. Thompson, and L. D. Nguyen

**Abstract**—A high-efficiency C-Band power amplifier design utilizing AlGaAs/InGaAs/GaAs *p*HEMT's is reported. On-wafer active loadpull power measurements at 4.5 GHz of a  $0.25\mu\text{m} \times 1.2\text{ mm}$  *p*HEMT exhibited an output power of 0.35 W and power-added efficiency of 79%. A single-stage MIC amplifier fabricated with a 2.8-mm-wide *p*HEMT resulted in  $P_{\text{out}} = 1.2\text{ W}$  and PAE = 74% at 4 GHz. These results demonstrate the potential of *p*HEMT's to significantly improve the efficiency performance of microwave solid state power amplifiers compared to present MESFET designs.

## I. INTRODUCTION

HIGH-EFFICIENCY power transistors are a critical building block of solid-state power amplifiers (SSPA's) for applications such as satellite communications systems. Even though there is new emphasis for satellite applications involving television broadcast at higher operating frequencies (i.e., Ku- and K-band), there is still a great need for improved performance of transponders at lower frequencies (i.e., C-Band) [1]. There exist additional high-performance, high-volume space applications at even lower frequencies (L- and S-Band) for new wide-area mobile communications systems. The GaAs-based metal-semiconductor field effect transistor has been considered the baseline power device for current C-Band SSPA applications [2], [3]. The potential for higher efficiency performance of heterojunction-based (HJ) devices, such as the pseudomorphic high electron mobility transistor *p*HEMT and the heterojunction FET (HFET), has resulted in significant interest in the HJ device technology for both microwave and millimeter-wave power applications (i.e., [4]–[6]).

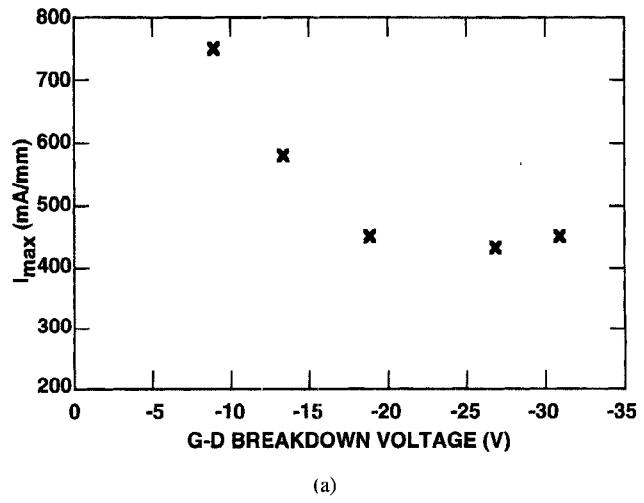

To achieve high power and efficiency simultaneously, a high breakdown voltage is required. The initial limitation of the HJ FET's at microwave frequencies was a characteristic low gate-drain breakdown voltage (i.e.,  $BV_{gd} < -10\text{ V}$ ). Researchers have implemented a double gate recess process [7] to increase the breakdown voltage competitive with the MESFET technology. A figure of merit for power FET's commonly used is the product of gate-drain breakdown voltage ( $BV_{gd}$ ) and full channel current ( $I_{\text{full}}$ ). A comparison of data achieved in our laboratory for different epitaxial layer designs to vary the maximum channel current, and therefore  $BV_{gd}$ , is shown in Fig. 1(a). These passivated *p*HEMT's

(a)

(b)

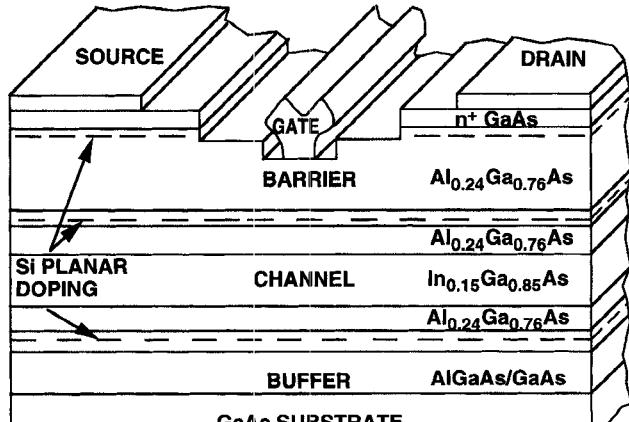

Fig. 1. (a) Cross section of *p*HEMT device structure and (b) variation of the device gate-drain breakdown voltage with maximum channel current.

were all processed in our laboratory with the same fabrication steps and the only variables were the sheet charge and both composition and thickness of the  $\text{In}_x\text{Ga}_{1-x}\text{As}$  channel layer. By reducing the doping and In composition from  $3.4 \times 10^{12} \text{ cm}^{-2}$  and 22% to  $2.4 \times 10^{12} \text{ cm}^{-2}$  and 15%, respectively, a reproducible breakdown voltage of  $|BV_{gd}| > 20\text{ V}$  is obtained. In this letter, the amplifier results obtained using this high breakdown voltage *p*HEMT device technology are reported.

Manuscript received August 18, 1995.

The authors are with the Hughes Research Laboratories, Malibu, CA 90265 USA.

Publisher Item Identifier S 1051-8207(96)00913-0.

## II. DEVICE STRUCTURE AND FABRICATION

The *p*HEMT structure reported in this work and shown in Fig. 1(b) was grown by molecular beam epitaxy (MBE). The structure is a triple-doped  $\text{Al}_{0.24}\text{Ga}_{0.76}\text{As}/\text{In}_{0.15}\text{Ga}_{0.85}\text{As}/\text{GaAs}$  *p*HEMT with two of the doping layers to supply the charge to the channel and the third Si-doping plane under the  $n^+$  GaAs contact cap layer to minimize access resistance. The double modulation doping scheme was implemented to achieve a sheet charge of  $n_s \sim 2.5 \times 10^{12} \text{ cm}^{-2}$ . The measured room temperature Hall sheet charge and mobility for this structure are  $2.38 \times 10^{12} \text{ cm}^{-2}$  and  $6700 \text{ cm}^2/\text{V} - \text{s}$ , respectively.

The device fabrication process begins with deposition of Ni/AuGe/Ag/Au source-drain ohmic contacts. A boron implantation process is then used to isolate the active region. Next, the ohmic contacts are alloyed at 420 °C for 30 seconds in a forming gas ambient. A specific contact resistance of 0.25 ohm-mm was obtained for this structure as compared to 0.32 ohm-mm for the double doped layer design. The gate recess process was then performed by a two-step nonselective etch process using a citric-acid based etchant. A source-drain spacing of 3  $\mu\text{m}$  and channel recess width of 1.5  $\mu\text{m}$  were found to result in the best combined dc and rf performance. The double recess etch process was developed using atomic force microscopy (AFM) to identify a reproducible wet chemistry and calibrate the resultant etch rate (8). The 0.25- $\mu\text{m}$  gates were formed by e-beam lithography and deposition of Ti/Pt/Au metalization. Finally, a 1000-Å layer of silicon nitride was deposited for device passivation and air-bridge interconnect metal fabricated. The wafer was thinned to 35  $\mu\text{m}$  to reduce the thermal resistance and backside vias formed to minimize source inductance.

## III. DEVICE AND AMPLIFIER PERFORMANCE

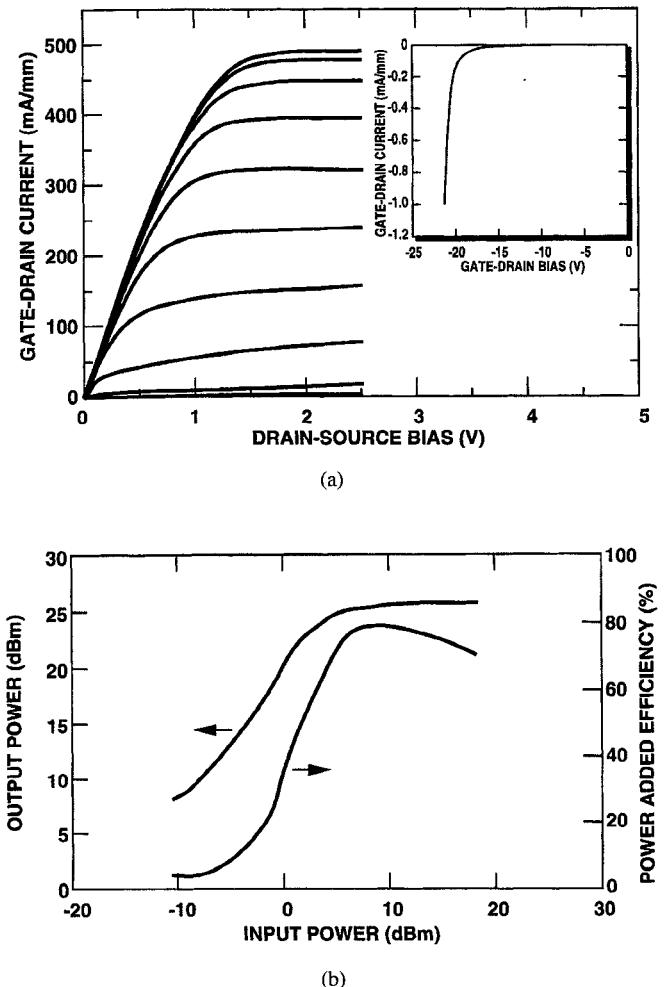

Devices were fabricated with total gate periphery of 0.4–19.8 mm. Fig. 2(a) shows the I-V characteristics of a 0.25  $\mu\text{m} \times$  0.4  $\mu\text{m}$ -wide *p*HEMT. The dc performance is characterized by a maximum transconductance of 280 mS/mm,  $I_{\text{full}} = 490 \text{ mA/mm}$ , and gate-drain breakdown voltage (source floating) of  $|BV_{gd}| = 21.5 \text{ V}$  measured at  $|I_{gd}| = 1 \text{ mA/mm}$  [see inset to Fig. 2(a)].

On-wafer power measurements were performed using an active load-pull CW measurement system [9] at 4.5 GHz. The measurement system is designed with independently adjustable loads to terminate the fundamental, second, and third harmonics for this measurement frequency. Devices with gate periphery of 1.2 mm were characterized with this system. The data was taken before the wafer was thinned or backside vias fabricated. Since the measurement was CW, sufficient power dissipation of the devices was of concern. However, the lateral and vertical path through the wafer for heat dissipation provided adequate heat sinking for the power levels reported here. The devices were biased at  $\sim 10\%$  of  $I_{\text{full}}$  for Class A-B operation. Drain-source bias was studied to optimize power-added efficiency (PAE) and output power ( $P_{\text{out}}$ ).

A plot of the on-wafer measured output power and PAE as a function of input power for  $V_{ds} = 5 \text{ V}$  is shown in Fig. 2(b). A

Fig. 2. (a) IV characteristic for a  $0.25 \times 400 \mu\text{m}^2$  *p*HEMT device and the gate-drain breakdown voltage curve. Here  $V_g$  is varied from  $+1.0 \text{ V}$  to  $-1.25 \text{ V}$  in steps of  $-0.25 \text{ V}$ . (b) On-wafer active load pull measurement if a  $0.25 \times 1200 \mu\text{m}^2$  *p*HEMT device demonstrating maximum efficiency and output power of 79% and 0.35 W, respectively.

maximum PAE of 79% is obtained at  $P_{\text{out}} = 25.4 \text{ dBm}$  (0.35 W, 0.29 W/mm). An improvement in of 8–10% was obtained by tuning the second harmonic (9 GHz) and 2–3% for the third harmonic (13.5 GHz) tuning. The data obtained with this measurement system assumes a conjugate input match for the device. Increasing  $V_{ds}$  to 7 V resulted in a significant increase of output power with a small decrease in PAE. Here, for  $V_{ds} = 7 \text{ V}$ , the measured data were PAE = 76%,  $P_{\text{out}} = 28.1 \text{ dBm}$  (0.65 W, 0.54 W/mm).

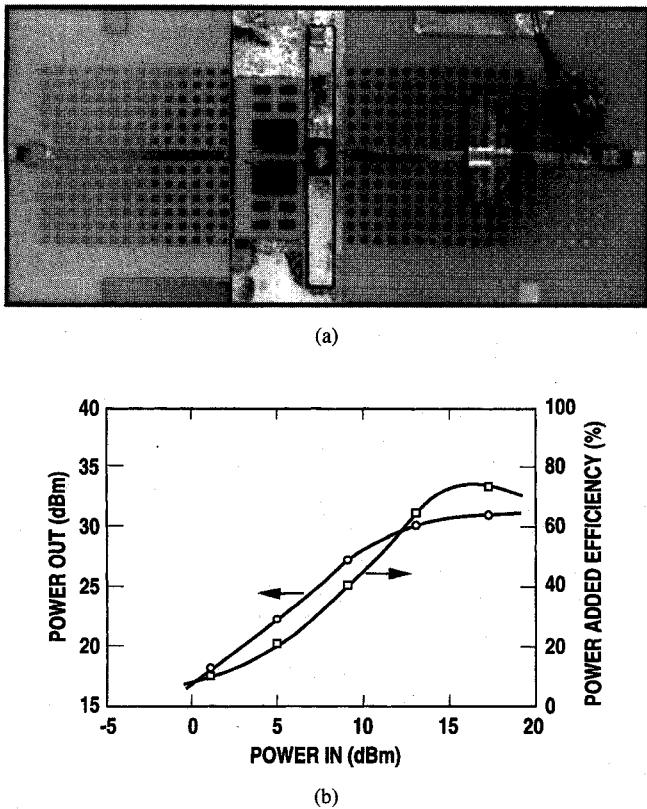

The load impedances measured for the 1.2-mm-wide *p*HEMT were scaled to estimate the optimum load impedances for a single-stage power amplifier with the 2.8-mm-wide device. The device technology demonstrated good power density scaling. In addition, the 2-terminal gate-drain breakdown voltage of the wider parts was comparable to the smaller gate periphery devices. A photograph of the 2.8-mm *p*HEMT amplifier is shown in Fig. 3(a). The measured RF power performance of this amplifier operating at 4 GHz is shown in Fig. 3(b). The measured output power at  $V_{ds} = 8 \text{ V}$  was 30.8 dBm (1.2W, 0.43 W/mm) with PAE = 74%.

Fig. 3. (a) Photograph of a 2.8-mm gate periphery pHEMT amplifier and (b) the measured efficiency and output power for this amplifier.

The output power for the 1.2 and 2.8 mm pHEMT amplifiers does not scale with device size since the biasing and tuning of the parts was not the same. The fundamental load impedance presented to the amplifier for best performance, however, scales well from the on-wafer result. In this initial circuit, the second and third harmonic terminations were close to the on-wafer values but not exactly the same. All efforts were made to minimize circuit losses in the rf and dc circuitry. Damping circuitry was used to make the amplifier critically stable in-band ( $K = 1, B_1 > 0$ ). A two-tone linearity measurement was made on the amplifier. For a two-tone input power equal to that needed to obtain maximum single carrier efficiency as above and with 2-MHz carrier spacing, the carrier to intermod (C/3IM) ratio was 14 dBc. All of the quoted amplifier numbers were made in a system calibrated from coaxial connector to connector with the  $V_{ds}$  measurement made at the bias probe external from the circuit.

#### IV. CONCLUSION

A high breakdown voltage GaAs-based pHEMT device technology has been reported. To the best of our knowledge, the reported on-wafer PAE of 79% for  $P_{out} = 0.35$  W is the highest-reported efficiency for a GaAs-based pHEMT operated at 4.5 GHz. The fabricated power amplifier obtained  $P_{out} = 1.2$  W with PAE of 74% at 4 GHz. This amplifier result, while slightly lower in efficiency than the on-wafer result (primarily due to matching circuit losses), represents a higher power density. Currently, amplifiers with single devices of total gate peripheries up to 25 mm are being fabricated. An output power of  $\approx 15$  W and efficiencies approaching 70% are predicted based on the performance reported in this letter.

#### ACKNOWLEDGMENT

The authors acknowledge the continued support of Dr. P. T. Greiling and Dr. M. Shahriary for this work. In addition, acknowledgement is given to Dr. B. Hughes and A. Cognata of Hewlett Packard for the on-wafer RF power measurement system. Finally, this work was supported by numerous valuable technical discussions with Dr. A. Berman, Dr. J. Greblunas, Dr. R. Rhodes and Dr. B. Walsh.

#### REFERENCES

- [1] *Space News*, vol. 5, no. 43, p. 1, Nov. 7-13, 1994.

- [2] J. Shu, J. Wei, R. Bassett, Y. Chung, C. Hua, C. Meng, P. Chye, J. Hall, and D. Day, "C-band high performance IMFETs and super IMFETs using MESFET and pHEMT technology for SATCOM applications," in *1994 IEEE/MTT-S Int. Microwave Symp.*, pp. 561-564.

- [3] T. Sonoda *et al.*, "High-efficiency and highly reliable 20 W GaAs power FET in C-band," *Jap. J. Appl. Phys.*, vol. 31, pp. 2374-2381, 1992.

- [4] A. K. Sharma, G. Onak, D. Yamauchi, D. I. Stones, J. Goel, R. Lai, and K. L. Tan, "Millimeter-wave high power amplifiers using pseudomorphic HEMT's," in *1994 MTT Symp. Dig.*, pp. 813-816.

- [5] L. Aucoin, S. Bouthillette, A. Platzker, S. Shanfield, A. Bertrand, W. Hoke, and Pl. Lyman, "Large periphery, high power pseudomorphic HEMTs," in *1993 GaAs IC Symp.*, pp. 351-353.

- [6] C. S. Wu, G. L. Lan, C. K. Pao, S. X. Bar, and M. Hu, "Pseudomorphic HEMT devices for microwave and millimeter wave applications," in *Proc. Mat. Res. Symp.*, vol. 300, 1993, pp. 41-54.

- [7] J. C. Huang, G. S. Jackson, S. Shanfield, A. Platzker, P. Saledas, and C. Weichert, "An AlGaAs/InGaAs pseudomorphic high electron mobility transistor with improved breakdown voltage for X- and Ku-band power applications," *IEEE Trans. Microwave Theory Tech.*, pp. 752-759, 1993.

- [8] J. J. Brown, J. Josefowicz, A. E. Schmitz, M. Thompson, and C. E. Hooper, "Atomic force microscopy structural analysis for the development of a manufacturable HEMT gate recess etch process," in *GaAs Manufacturing Technology Conf.*, 1995, pp. 171-174.

- [9] B. Hughes, A. Ferrero, and A. Cognata, "Accurate on-wafer power and harmonic measurements of mm-wave amplifiers and devices," in *IEEE MTT-S, Int. Microwave Symp. Dig.*, 1992, pp. 1019-1022.